页表项详解

以下介绍基于IA-32e (x86_64),参考 “Intel® 64 and IA-32 Architectures Software Developer’s Manual”

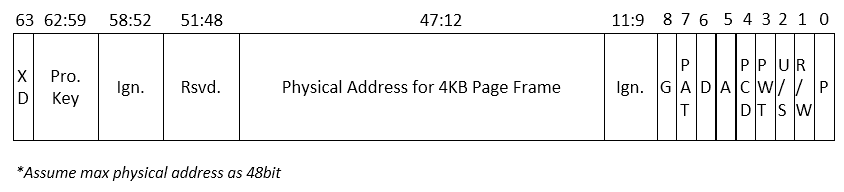

页表是实现地址翻译的重要结构,其中,Page Table Entry (PTE)存储了页帧的物理地址和控制标记,了解PTE的详细结构对理解访存过程中的权限控制、缺页处理等机制都有着重要的意义。

PTE的内部结构如下图所示:

关键控制位的详细解释

| 比特位 | 简称 | 说明 |

|---|---|---|

| 0 | P | 表示页帧是否存在;如果P值为0,访问该页帧将触发 Page Fault |

| 1 | R/W | 表示页帧的读写权限;如果值为0,表示页帧不能被修改(R/W生效,依赖CR0 Write Protect比特置位 |

| 2 | U/S | 表示页帧对用户态和内核态访问的限制;如果值为0, 不允许用户态访问 |

| 3 | PWT | PAT,PCD和PWT位组成Page Attribute Table的索引,表示页帧的缓存模式 |

| 4 | PCD | 见PWT说明 |

| 5 | A | 表示PTE是否被访问过;若处理器在地址翻译的过程中使用了该PTE,则置位该PTE的A位 |

| 6 | D | 表示页帧被修改过;若处理器发现对线性地址的写操作,置位对应PTE的D位 |

| 7 | PAT | 见PWT说明 |

| 8 | G | 表示页帧为全局页,TLB中该页帧对应的地址转换,不会在进程切换时清空 |

- A位和D位只能由软件清除